### **RESEARCH ARTICLE**

## Design of fault-tolerant reversible Vedic multiplier in quantum cellular automata

**A. Kamaraj<sup>1\*</sup> and P. Marichamy<sup>2</sup>** <sup>1</sup> Department of Electronics and Communication Engineering, Mepco Schlenk Engineering College, Sivakasi, India.

<sup>2</sup> Department of Electronics and Communication Engineering, P.S.R. Engineering College, Sivakasi, India.

Submitted: 03 November 2018; Revised: 23 May 2019; Accepted: 28 June 2019

Abstract: In modern computational technologies, a major challenge is the design of devices with smaller size, low power dissipation, and high speed. In order to achieve better optimisation in power dissipation, size and speed, it is necessary to find a technological change. Researchers are trying to find ways and means by introducing many architectural and behavioural changes in the available technologies. One such possible solution is to design digital circuits based on reversible logic and implement them in quantum cellular automata (QCA). In a multiplication process, partial product generation and the addition of partial products are the major factors contributing to the propagation delay. In this paper, Urdhwa Triyakbhyambased Vedic multiplier using reversible logic is proposed. Vedic multipliers result in faster partial products with less number of steps. Ripple carry adders are used for adding the partial product results to obtain the final product. The multiplier modules are constructed using fault-tolerant reversible KMD gates and hence, the proposed multiplier is a fault-tolerant Vedic multiplier. The designed multiplier is realised in QCA. In the proposed reversible Vedic multiplier, quantum cost is reduced up to 72 %, garbage output is reduced up to 87 %, constant input is reduced up to 87 % and the number of gates are reduced up to 57 % compared to the existing conventional and Vedic multipliers.

Keywords: KMD gates, reversible logic, Urdhwa Triyakbhyam, Vedic multiplication.

### INTRODUCTION

In computing, every computing system needs to be optimised in power dissipation, area and speed to be efficient. It is very difficult to achieve all three parameters in a single step with the currently available Complementary Metal Oxide Semiconductor (CMOS) technologies. Moreover, scaling of CMOS limits its performances in many dimensions such as current leakage, noise, interconnections, etc. Hence, it is desirable to move on to other technologies to achieve computational efficiency. Reversible logic-based computation is a better alternative to move towards effective computing systems.

In 1961, Launder invented that losing a bit of information causes heat in the order of kTln2 Joules (where, k - Boltzmann's constant and T - absolute temperature) (Landauer, 1961). This heat is generated due to the bit loss in conventional computation. In 1973, Bennett proposed the reversible logic-based computation, which has a one-to-one unique mapping between the input and output (Bennett, 1973) i.e. the number of inputs and outputs are same. Hence, the kTln2 Joules of heat dissipation is avoided.

Fault detection and avoidance are major problems in digital circuits and it could be achieved by designing a fault-tolerant circuit. Fault-tolerance could be achieved by parity preservation, which means to have an equal parity in inputs and outputs; i.e., exclusive OR gate (XOR) of all the inputs and outputs must be equal (Behrooz, 2006). Therefore, for a reversible logic circuit to be fault-tolerant, it should have parity preservation.

Corresponding author (kamarajvlsi@gmail.com; 10 https://orcid.org/0000-0001-6952-2374)

This article is published under the Creative Commons CC-BY-ND License (http://creativecommons.org/licenses/by-nd/4.0/). This license permits use, distribution and reproduction, commercial and non-commercial, provided that the original work is ND properly cited and is not changed in anyway.

In a computing system, one of the complicated and time-consuming computations is multiplication. Many researchers have proposed different methods for multiplication in order to speed up the computation of the multiplier. Some of the currently available multipliers are designed with carry-save adder (CSA), carry-select adder and carry-skip adders for fast product generation. Later, special multipliers such as Baugh Wooley multiplier, Wallace multiplier, serial / parallel multiplier and Booth multipliers (Hamacher *et al.*, 2011) have been introduced to speed up the process. However, neither the complexity nor the critical path delay in the multiplication process is reduced.

A better alternative solution is Vedic multiplication, which is an ancient way of performing multiplication. Vedic mathematics is reinvented by Sri Bharati Krisna Tirtha from the Indian Veda scriptures. It has 16 sutras and out of them *Nikhilam Sutram*, *Urdhva Tiryakbhayam*, and *Anurupye* are the most popularly used sutras. The advantage of the Vedic multiplier is that it has very simple procedures for complex multiplication (Rakshith *et al.*, 2013). The multiplication could be extended to n-bits with some minor modifications.

A n×n reversible Vedic multiplier is proposed and implemented in field-programmable gate array (FPGA) and its resource utilisation is discussed in Poornima *et al.* (2013). A reversible logic-based *Urdhva Tiryakbhyam* multiplication algorithm is implemented in FPGA. Peres, BME and Toffoli gates are utilised to construct the reversible 4×4 Vedic multiplier (Shivarathnamma *et al.*, 2016). In Srikanth *et al.* (2014) a 32-bit reversible Vedic multiplier based on *Urdhva Tiryakbhayam* sutra is designed with Peres, HNG and Feynman gate. Here also, Verilog HDL-based design was implemented in FPGA and the delay and power dissipation were analysed.

A 4-bit reversible Vedic multiplication is implemented in FPGA. The multiplier is constructed with Peres, Feynman and NFT gates, in which NFT is a fault-tolerant gate (Rakshith & Saligram, 2013). In this paper, reversible logic performance measures (quantum cost, constant input, garbage outputs) are considered. In Haghparast *et al.* (2009), MKG and HNG reversible gates are introduced for the optimisation in reversible multiplication. The partial product generation is completed with the Peres, HNG gates. More significantly, hardware complexity of the multiplier is measured using logical calculation and a quantum circuit of the gates are introduced.

More recently, a new type of parity preserving gates was analysed (Valinataj, 2017). Here parity preserving

gates, double Feynman, Fredkin, NFT, MIG, double Peres and ZPLG ( $5\times5$ ) are discussed. These gates are otherwise named as conservative gates or fault-tolerant gates. A signed multiplier is constructed using these fault-tolerant gates but the multiplier works based on the conventional array multiplication. Thus, its number of gates increases, thereby its hardware complexity is also a little high (Valinataj, 2017).

A detailed procedure to conduct the *Urdhva Tiryagbhyam Sutra*-based Vedic multiplication is explained by (Subramanian *et al.*, 2016). An 8-bit multiplier is designed with conventionally available reversible gates such as Peres and Feynman gates. This multiplier acts as a part of the arithmetic logic unit. Further, their performance measures are done using reversible logic parameters (Subramanian *et al.*, 2016). The Vedic multiplication costs lower than the booth multiplication.

In Poornima *et al.*, (2013), Shivarathnamma *et al.*, (2016), Srikanth and Nasam (2016) and Saligram and Rakshith (2013), the final implementation is carried out on FPGA. Since it is a transistor-based approach, low power cosumption and reversibility cannot be assured. The reversible Vedic multiplier were constructed by Rakshith (2013), Haghparast (2009) and Subramanian *et al.* (2016) but they are not fault-tolerant. The fault-tolerant gate was used only by Valinataj (2017), for designing conventional multiplier. Till now, no multiplier was constructed with fault tolerance, reversibility, and realisation in QCA. Hence, the proposed fault-tolerant

The paper first describes the currently available reversible gates and reviews multipliers. Then it explains the reversible logic metrics and QCA and illustrates the proposed reversible KMD gates and its quantum realisation. Thereafter, the steps of Vedic multiplication process and its QCA realisations are explained. Finally, it compares the conventional multipliers and existing Vedic multipliers with the proposed fault-tolerant reversible Vedic multiplier and concludes the paper stating the usefulness of *Urdhva Tiryakbhayam* multiplier.

### METHODOLOGY

### **Reversible logic metrics and QCA**

A reversible gate is expected to have a distinctive mapping between its inputs and outputs; i.e., bijective. It is known as reversibility. In addition, if a reversible gate is capable of generating NOT, AND/NAND & OR/ NOR functions, it is said to be a universal reversible gate (Kalyan, 2014).

The XOR function of inputs and outputs of the reversible gate has to be equal to a fault-tolerant reversible gate [11]. It is otherwise named as parity preservation or conservative logic. Considering  $I_i$ 's are inputs and  $O_i$ 's are outputs of a reversible gate, then it should satisfy the following equation (1),

$$I_1 \bigoplus I_2 \bigoplus I_3 \dots \bigoplus I_n = O_1 \bigoplus O_2 \bigoplus O_3 \dots \bigoplus O_n \qquad \dots (1)$$

Reversible logic measures slightly deviate from conventional measure metrics. The commonly used reversible logic metrics are quantum cost, garbage output, constant input, and logical calculations.

These metrics are defined as follows,

### Quantum cost:

It is the number of  $1 \times 1$  and  $2 \times 2$  primitive gates used to realise the desired reversible logic function (Valinataj, 2017).

### Garbage output:

The number of outputs not utilised to promote computation is known as garbage output. It is mainly used to maintain the reversibility (Poornima *et al.*, 2013).

### Constant input:

It is defined as a stable value (either logical '0' or '1') set in the input of the reversible gate throughout the computation to derive the desired logical output (Poornima *et al.*, 2013).

### Logical calculation:

It is a measure of the number of XOR ( $\alpha$ ), AND ( $\beta$ ) and NOT ( $\delta$ ) gate functions mandatory to obtain the reversible logic circuit (Haghparast *et al.*, 2009).

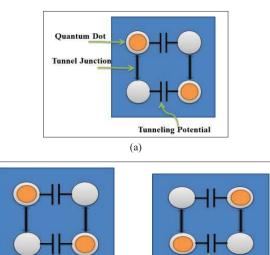

The realisation of the reversible circuit is performed in quantum cellular automata (QCA). It is a quantum cell consisting of four quantum dots. The position of the electrons defines the logical state of the cell (either logic '0' or '1'). The electrons always occupy diagonally opposite positions as shown in Figure 1 (a, b).

The dimension of the quantum cell is in the order of nanometers. The quantum cellular automata have two major advantages. They are,

i. The computation and information flow (signal propagation) take place simultaneously. It makes the computation and communication faster in QCA.

ii. Each quantum cell is behaving as a computation unit as well as an interconnection line. Therefore, no separate interconnection lines are required.

Because of these two advantages, QCA-based implementation of fault-tolerant reversible logic circuits provides efficiency in power consumption, area, and speed of computation (Sridharan & Pudi, 2015).

(b)

Logic '1' (P=+1)

Figure 1: QCA cell polarised with Logic '0' and Logic '1'

Logic '0' (P=-1)

# Proposed reversible KMD gates and its QCA realisation

Many researchers are proposing new reversible gates when there is a need to design reversible circuits at an optimum cost. It would be done by either proposing a novel reversible gate or using the combination of available reversible gates configuration. Some of the proposed reversible gates are BME (Shivarathnamma *et al.*, 2016), MRG, DKG (Biswas *et al.*, 2014), NFT (Rakshith & Saligram, 2013; Ali *et al.*, 2015), TSG, MKG, HNG (Haghparast *et al.*, 2009), MIG and ZPLG (Valinataj, 2017). These gates mostly satisfy reversibility and universality, but they rarely have the property of fault-tolerance. The characteristics of the proposed and existing reversible gates are shown in Table 1.

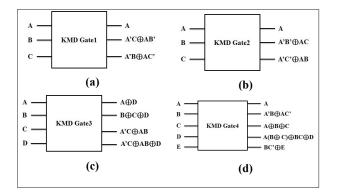

In this paper, four fault-tolerant reversible KMD gates are proposed. These gates have reversibility, universality, and fault-tolerance (parity preservation) properties (Kamaraj & Marichamy, 2018). The configuration of KMD gates are depicted in Figure 2 (a, b, c, d).

| S. No. | Reversible | No. of       | Reversibility | Universality | Fault     | Hardware                     |

|--------|------------|--------------|---------------|--------------|-----------|------------------------------|

|        | gate       | IOs          |               |              | tolerance | complexity                   |

| 1.     | Feynman    | $2 \times 2$ | Yes           | Yes          | No        | 1α                           |

| 2.     | Fredkin    | $3 \times 3$ | Yes           | Yes          | No        | 2α+4β+1γ                     |

| 3.     | Toffoli    | $3 \times 3$ | Yes           | Yes          | No        | 1α+1β                        |

| 4.     | Peres      | $3 \times 3$ | Yes           | Yes          | No        | $2\alpha + 1\beta$           |

| 5.     | HNG        | $4 \times 4$ | Yes           | Yes          | No        | 5α+2β                        |

| 6.     | MRG        | $4 \times 4$ | Yes           | Yes          | No        | $4\alpha + 1\beta$           |

| 7.     | DKG        | $4 \times 4$ | Yes           | Yes          | No        | 5α+4β+2γ                     |

| 8.     | MKG        | $4 \times 4$ | Yes           | Yes          | No        | 4α+2β+3γ                     |

| 9.     | TSG        | $4 \times 4$ | Yes           | Yes          | No        | $3\alpha + 1\beta$           |

| 10.    | BME        | $4 \times 4$ | Yes           | Yes          | No        | $4\alpha + 3\beta + 1\gamma$ |

| 11.    | MIG        | $4 \times 4$ | Yes           | Yes          | Yes       | $3\alpha + 2\beta + 1\gamma$ |

| 12.    | NFT        | $3 \times 3$ | Yes           | Yes          | Yes       | 3α+3β+2γ                     |

| 13.    | ZPLG       | $5 \times 5$ | Yes           | Yes          | Yes       | 8α+3β+1γ                     |

| 14.    | KMD gate 1 | $3 \times 3$ | Yes           | Yes          | Yes       | 2α+4β+3γ                     |

| 15.    | KMD gate 2 | $3 \times 3$ | Yes           | Yes          | Yes       | 2α+4β+3γ                     |

| 16.    | KMD gate 3 | 4× 4         | Yes           | Yes          | Yes       | 5α+3β+1γ                     |

| 17.    | KMD gate 4 | $5 \times 5$ | Yes           | Yes          | Yes       | 6α+4β+2γ                     |

Table 1:

Reversibility, universality and fault tolerance of reversible gates

Figure 2: Functional diagram: (a) KMD gate 1; (b) KMD gate 2; (c) KMD gate 3 and (d) KMD gate 4

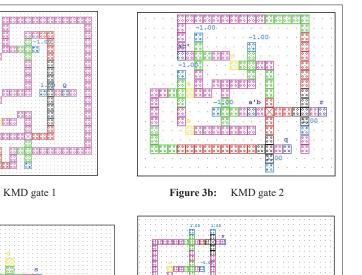

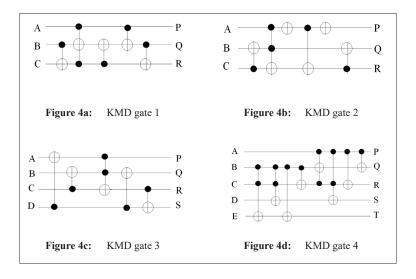

The KMD gates need a minimum number of cells for its realisation in QCA compared to the previously proposed reversible gates. From Table 2, it is observed that KMD gates require a minimum number of cells for its realisation, and therefore the area occupied gets minimised. The QCA realisation and quantum structure of KMD gates are shown in Figures 3 and 4, respectively.

### **Vedic multiplier**

The literal meaning of *Urdhva Tiryagbhyam Sutra* is 'Vertically and Crosswise'. It performs multiplication in vertical and crosswise and the partial products are

| Table 2: | Comparison of the cost of the KMD gates |

|----------|-----------------------------------------|

|          |                                         |

| Reversible gates                       | Number of cells used | Quantum<br>cost | Area<br>(µm <sup>2</sup> ) |

|----------------------------------------|----------------------|-----------------|----------------------------|

| Fredkin gate (Biswas et al., 2014)     | 187                  | 5               | 0.19                       |

| DKG gate (Biswas et al., 2014)         | 752                  | 6               | 1.24                       |

| MRG GATE (Biswas et al., 2014)         | 456                  | 6               | 0.52                       |

| NFT gate (Ali et al., 2015)            | 128                  | -               | 0.142                      |

| KMD gate 1 (Kamaraj & Marichamy, 2018) | 169                  | 10              | 0.19                       |

| KMD gate 2 (Kamaraj & Marichamy, 2018) | 121                  | 10              | 0.13                       |

| KMD gate 3 (Kamaraj & Marichamy, 2018) | 116                  | 6               | 0.19                       |

| KMD gate 4 (Kamaraj & Marichamy, 2018) | 244                  | 12              | 0.42                       |

E 00 0000000

Figure 3a:

Figure 3c: KMD gate 3 Figure 3d: KMD gate 4

Figure 3: QCA realisation of KMD gates

Figure 4: Quantum structure of KMD gates

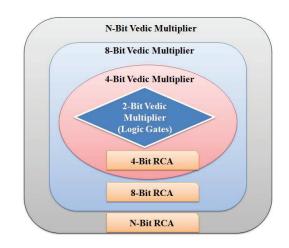

summed to generate the final result. The basic module of the sutra is  $2\times 2$  Vedic multiplier and adder. The repeated arrangement of the  $2\times 2$  multiplier would

derive the construction of n-bit multiplication. Thus, the computation is very fast as this requires a much less number of steps (Kamaraj *et al.*, 2017).

### Procedure for Vedic multiplication:

- 1. The least significant bit of the two numbers is multiplied to form the LSB of the result (vertical).

- 2. The next higher bits are cross multiplied with each other and the results are added together to produce the next digit of multiplication.

- 3. The carry part of step 2 is added to the next level sum output to form the next higher bit.

- 4. All the bits are processed in the same way as in step 2 and step 3 until the last digit of the operand is reached.

- 5. Record the final product of the Vedic multiplication.

### 2×2 Vedic multiplier

A two bit multiplication of the two numbers A×B could be carried out in the following manner. The logical expression of the final product is,

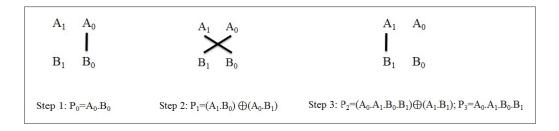

$$\begin{split} & P_0 = A_0 \cdot B_0; \\ & P_1 = (A_1 \cdot B_0) \bigoplus (A_0 \cdot B_1); \\ & P_2 = (A_0 \cdot A_1 \cdot B_0 \cdot B_1) \bigoplus (A_1 \cdot B_1); \\ & P_3 = A_0 \cdot A_1 \cdot B_0 \cdot B_1 \end{split}$$

It requires 4 AND operations and 2 ADD operations. Graphically, it is represented as in Figure 5.

**Figure 5:** Graphical representation of 2×2 Vedic multiplication steps

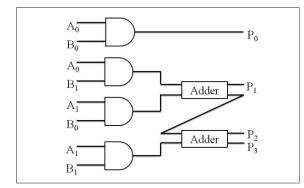

Figure 6a: The hardware architecture of 2-bit Vedic multiplier

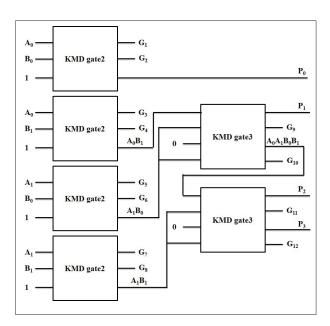

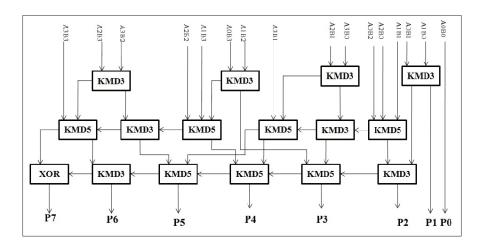

The corresponding hardware architecture of the  $2\times2$ Vedic multiplier is depicted in Figure 6a. It has logical AND gates and adders for calculating the product terms. Fault tolerant reversible KMD gates structure of the Vedic multiplier is shown in Figure 6b. In this structure all the functional modules are designed using KMD gates only.

**Figure 6b:** The reversible logic structure of 2×2 Vedic multiplier using KMD gates

### 4×4 Vedic multiplier

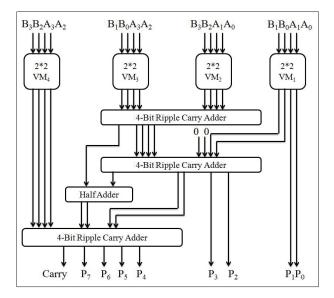

The 4-bit Vedic multiplier (VM) module is constructed using the 2-bit Vedic multiplier unit (VM<sub>i</sub>) four times, three 4-bit ripple carry adders and one half adder gate, which are shown in Figure 7. The inputs  $A_i (A_3A_2A_1A_0)$ and  $B_i (B_3B_2B_1B_0)$  are specified to 2-bit Vedic multiplier bitwise, and then the multiplier output is forwarded to the 4-bit RCA adder. The output from the RCA adder consists of 4-bit sum output and a 1-bit carry value. The half adder is used to sum the carry at the first two phases of ripple carry adder. The output of 4-bit multiplier consists of 8-bit product term ( $P_i - P_7 ... P_0$ ) (Gowthami & Satyanarayana, 2018).

In a similar way, higher order Vedic multipliers are constructed with the 2-bit VM<sub>i</sub> as the base module and

Figure 7: The hardware structure of 4-bit Vedic multiplier

RCA adders for summation of the partial products. The n-bit Vedic multiplier uses four n/2-bit multipliers, one n-bit RCA adder, one n-bit full adder, and one [(n/2)-1] bit RCA adder (using only half adder). For example, construction of 16-bit Vedic multipliers by this comprehensive structure requires four 8-bit multiplier units, one 16-bit RCA adder, one 16-bit full adder, and one 7-bit RCA adder (using only half adder). General n-bit Vedic multiplication unit construction using this is illustrated in Figure 8 (Kamaraj *et al.*, 2018b).

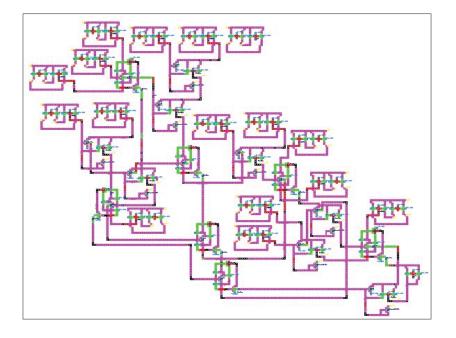

### QCA realisation of reversible Vedic multiplier

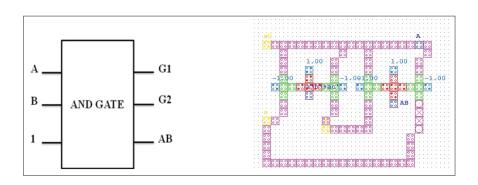

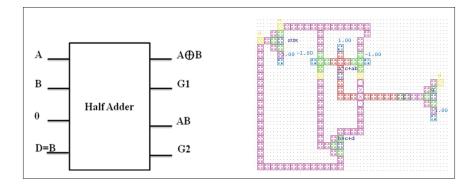

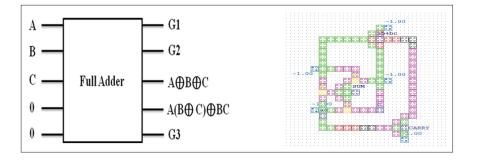

The necessary modules for designing a multiplier are AND gate, half adder, and a full adder. These functions could be derived from KMD gates. The reversible Vedic multiplier modules are designed with fault-tolerant reversible gates and it is called fault-tolerant reversible Vedic multiplier.

Figure 8: Generalised construction of n-bit Vedic multiplier

Figure 9: Fault-tolerant reversible AND gate and QCA structure using KMD gate 2

Figure 10: Fault-tolerant reversible half adder and QCA structure using KMD gate

Figure 11: Fault-tolerant reversible full adder and QCA structure using KMD gate 4

Figure 12: Proposed fault tolerant reversible Vedic multiplier

### Fault-tolerant reversible AND gate

By setting logic '1' in the third input of KMD gate 2, AND gate function is derived. The remaining outputs

are called garbage outputs (G). In that way, many logical functions can be derived from the single gate. Figure 9 shows the schematic diagram and QCA realisation of AND gate using KMD gate 2.

Figure 13: QCA structure of proposed fault tolerant reversible Vedic multiplier

### Fault-tolerant reversible half adder

By setting logic '0' in the third input of KMD gate 3 and fourth input as a second input (B), the half adder can be obtained. The remaining outputs are called garbage outputs (G). Figure 10 shows the schematic diagram of half adder using KMD gate 3 and its QCA realisation.

### Fault-tolerant reversible full adder

Constant input logic '0' set at fourth and fifth input of KMD gate 4, would make it a full adder. The remaining outputs are called garbage outputs (G). Figure 11 shows the schematic diagram of full adder using KMD gate 4 and its QCA realisation.

### Fault-tolerant reversible Vedic multiplier

The fault-tolerant reversible Vedic multiplier is constructed using three KMD gates. In this multiplier, the multiplication process includes only six steps. The addition process is computed by using KMD gates. Here KMD gates 2, 3 and 4 are used to generate the AND function, half adder and full adder, respectively. The fault tolerant reversible Vedic multiplier using KMD gates and its corresponding QCA structure is given in Figures 12 and 13, respectively.

### **RESULTS AND DISCUSSION**

The 4-bit Vedic multiplier depicted in Figure 7 has been constructed using Fault-tolerant reversible KMD gates as shown in Figure 12. The corresponding QCA architecture is designed in QCA designer 2.0.3. Fault-tolerance of the Vedic multiplier has been achieved in two ways: (i) designing it fully with Fault-tolerant KMD gates and (ii) constructing with a combination of fault-tolerant KMD and conventional reversible gates (Fredkin, Toffoli). In both of these approaches, the Vedic multiplier is a faulttolerant reversible multiplier.

The  $2\times 2$  Vedic multiplier has AND gate and half adders as described in the previous section. The total cost for construction in approach 1 is 110. Similarly, the higher order multipliers are constructed from the lower order multipliers. The cost calculation of individual modules of the multiplier and the total costs are listed in Table 3. The total cost includes the sum of quantum cost, garbage output, constant inputs and the number of gates.

In approach 2, the AND gate is constructed using a Fredkin gate instead of KMD gates. However, it is a fault-tolerant reversible multiplier. The cost calculation of individual units and the total costs are shown in Table 4.

| Functional module | Quantum<br>cost    | Garbage<br>output | Constant<br>input | Number of<br>gates<br>(primitive) | Number of gates | Total cost<br>(QC + GO +<br>CI + NoG) | Logical calculations            |

|-------------------|--------------------|-------------------|-------------------|-----------------------------------|-----------------|---------------------------------------|---------------------------------|

| 2-bit fault-toler | ant reversible Veo | dic multiplier    |                   |                                   |                 |                                       |                                 |

| AND gate          | 10                 | 2                 | 1                 | 6                                 | 1               | 19                                    | $2\alpha + 4\beta + 3\gamma$    |

| Half adder        | 9                  | 2                 | 1                 | 5                                 | 1               | 17                                    | $5\alpha+2\beta+1\gamma$        |

| Full adder        | 22                 | 3                 | 2                 | 8                                 | 1               | 35                                    | $6\alpha + 5\beta + 2\gamma$    |

| 2-bit VM          | 58                 | 12                | 6                 | 34                                | 6               | 110                                   | $18\alpha + 20\beta + 14\gamma$ |

| 4-bit fault-toler | ant reversible Veo | dic multiplier    |                   |                                   |                 |                                       |                                 |

| 4-bit adder       | 88                 | 12                | 8                 | 32                                | 4               | 140                                   | 24α+20β+8γ                      |

| 4-bit VM          | 496                | 84                | 48                | 232                               | 36              | 860                                   | 144α+140β+80γ                   |

### Table 3: Performance of fault-tolerant reversible Vedic multiplier (Approach 1)

Table 4:

Performance of fault-tolerant reversible Vedic multiplier (Approach 2)

| Functional<br>module     | Quantum<br>cost | Garbage<br>output | Constant<br>input | Number of<br>gates<br>(primitive) | Number of gates | Total cost<br>(QC + GO +<br>CI + NoG) | Logical calculation            |

|--------------------------|-----------------|-------------------|-------------------|-----------------------------------|-----------------|---------------------------------------|--------------------------------|

| 2-bit fault-tolerant rev | ersible Vedic n | nultiplier        |                   |                                   |                 |                                       |                                |

| AND gate (Fredkin)       | 3               | 2                 | 1                 | 1                                 | 1               | 6                                     | $2\alpha + 4\beta + 1\gamma$   |

| Half adder               | 9               | 2                 | 1                 | 5                                 | 1               | 12                                    | $5\alpha+2\beta+1\gamma$       |

| Full adder               | 22              | 3                 | 2                 | 8                                 | 1               | 27                                    | $6\alpha + 5\beta + 2\gamma$   |

| 2-bit VM                 | 30              | 12                | 6                 | 14                                | 6               | 48                                    | $18\alpha + 20\beta + 8\gamma$ |

| 4-bit fault-tolerant rev | ersible Vedic n | nultiplier        |                   |                                   |                 |                                       |                                |

| 4-bit adder              | 88              | 12                | 8                 | 32                                | 4               | 108                                   | 24α+20β+8γ                     |

| 4-bit VM                 | 384             | 84                | 48                | 152                               | 36              | 516                                   | $144\alpha + 140\beta + 43$    |

Table 5:

Performance comparison of existing multipliers with proposed multiplier

| Performance             | Conventiona     | l multipliers              | V                               | Vedic multiplier                | •                                    | Proposed Vedic | e multiplier |

|-------------------------|-----------------|----------------------------|---------------------------------|---------------------------------|--------------------------------------|----------------|--------------|

| measures                | Valinataj, 2017 | Haghparast<br>et al., 2009 | Saligram<br>& Rakshith,<br>2013 | Rakshith<br>& Saligram,<br>2013 | Gowthami &<br>Satyanarayana,<br>2018 | Approach 1     | Approach 2   |

| Quantum cost            | 177             | 137                        | 164                             | 162                             | 128                                  | 110            | 48           |

| Garbage output          | 49              | 28                         | 43                              | 62                              | 40                                   | 12             | 12           |

| Constant input          | 49              | 28                         | 33                              | 29                              | 31                                   | 6              | 6            |

| Number of gates         | 28              | 28                         | 33                              | 37                              | 31                                   | 14             | 14           |

| Logical calculations    | 128α+78β+28γ    | 71α+36β                    | -                               | -                               | -                                    | 18α+20β+14γ    | 18α+20β+8γ   |

| area (µm <sup>2</sup> ) | -               | -                          | -                               | -                               | -                                    | 3.7            | 3.7          |

(Gowthami & Satyanarayana, 2018)

(Rakshith & Saligram, 2013) Approach 1 Approach 2

(Saligram & Rakshith, 2013) Approach 1 Approach 2

(Haghparast et al., 2009) Approach 1 Approach 2

(Valinataj, 2017) Approach 1 Approach 2

HNG

ZPLG

Conventional multipliers using

Performance

measures

HNG and NFT

HNG

Vedic multiplier using

% of improvement of the proposed multiplier w.r.t.

BME and HNG

Approach 1 Approach 2

| 37.85 % 72.88 % | 19.70 % 64.96 % | 32.92 % 70.73 % | 32.09 % 70.37 % | 14.06 % 62.5 % |

|-----------------|-----------------|-----------------|-----------------|----------------|

| 75.51 %         | 57.14 %         | 72.09 %         | 80.64 %         | 70 %           |

| 87.75 %         | 78.57 %         | 81.81 %         | 79.31 %         | 80.64 %        |

| 50 %            | 50 %            | 57.57 %         | 62.16 %         | 54.83 %        |

Number of gates

Constant input

Garbage output

Quantum cost

The designed fault-tolerant reversible Vedic multiplier cost performance was compared with the existing conventional and reversible Vedic multipliers and they are shown in Table 5. The performance of the proposed method shows an improvement compared to the existing multipliers in terms of quantum cost, garbage output, constant input, and logical calculations. The percentage of improvement is shown in Table 6 with respect to the existing multipliers.

### CONCLUSION

In general, computation speed of a system is based on the hardware architecture and the data path design. In this paper, an Urdhwa Triyakbhyam-based Vedic multiplier has been designed in reversible logic. Vedic multipliers perform computations in minimum number of steps and therefore faster. The necessary functional modules are AND logic, half adder and full adder. These functional modules are constructed in two different approaches. In the first approach all the functional modules are constructed using fault tolerant reversible KMD gates only, and in the second approach combination of Fredkin and KMD gates are used. The functional simulation is performed in QCA environment using QCADesigner 2.0.3. The performance measure shows that the proposed fault-tolerant reversible Vedic multiplier has improved in quantum cost (14 - 72 %), garbage output (57 - 80 %), constant input (78 - 87 %), and a number of gates (50 - 7%)62 %) compared to the existing design. Further, its logical calculation or hardware complexity is  $13\alpha + 11\beta + 6\gamma$ , which is comparable with the existing design. Thus, it is concluded that the computation speed and efficiency can be improved by crosswise and vertical multiplication for the proposed fault-tolerant reversible Vedic multiplier.

### REFERENCES

- Bahar A., Ahmed S. & Hossain N. (2015). A new approach of presenting reversible logic gate in nano-scale. Springer Plus 4(153): 1–7.

- DOI: https://doi.org/10.1186/s40064-015-0928-4.

- Behrooz P. (2006). Fault-tolerant reversible circuits. Proceedings of 40<sup>th</sup> Asilomar Conference Signals, Systems, and Computers, Pacific Grove, CA, pp. 1726–1729.

- Bennett C.H. (1973). Logical reversibility of computation. *IBM Journal of Research and Development* 17: 525–532. DOI: https://doi.org/10.1147/rd.176.0525

- Biswas P., Gupta N. & Patidar N. (2014). Basic reversible logic gates and it's QCA implementation. *International Journal of Engineering Research and Applications* 4(6): 12–16.

# Fable 6: Percentage of improvement of the proposed multiplier

- Gowthami P. & Satyanarayana R.V.S. (2018). Performance evaluation of reversible Vedic multiplier. ARPN Journal of Engineering and Applied Sciences 13(3): 1002–1008.

- Haghparast M., Mohammadi M., Navi K. & Eshghi M. (2009).

Optimized reversible multiplier circuit. *Journal of Circuits, Systems, and Computers* 18(2): 311–323.

DOI: https://doi.org/10.1142/s0218126609005083

- Hamacher C., Vranesic Z. & Zaky S. (2011). *Computer Organization*, 5<sup>th</sup> edition, Tata McGraw-Hill, New York, USA.

- Kalyan P.S. (2014). *Introduction to Reversible Computing*, 1<sup>st</sup> edition. Chapman & Hall/CRC Press, Tennessee, USA.

- Kamaraj A., Daisy P.A. & Priyadharshini V. (2017). Realization of Vedic sutras for multiplication in Verilog. *International Journal of VLSI and Signal Processing* 4(1): 25–29.

- Kamaraj A. & Marichamy P. (2018a). Design of faulttolerant reversible floating point division. *Journal of Microelectronics, Electronic Components and Materials* 48(3): 169–179.

- Kamaraj A., Pavi N.M., Nandhini T. & Marichamy P. (2018b). Design of fault tolerant reversible multipliers using novel reversible gates, 2<sup>nd</sup> International Conference on Applied Soft Computing Techniques (ICASCT), pp. 473–476.

- Landauer R. (1961). Irreversibility and heat generation in the computing process. *IBM Journal of Research and Development* 5(3): 183–191. DOI: https://doi.org/10.1147/rd.53.0183

- Poornima M., Shivaraj Kumar P., Shivukumar, Shridhar K.P. & Sanjay H. (2013). Implementation of multiplier using Vedic

- algorithm. International Journal of Innovative Technology and Exploring Engineering (IJITEE) **2(**6): 219–223.

Rakshith T.R. & Saligram R. (2013). Design of high speed low power multiplier using reversible logic: a Vedic mathematical approach. *International Conference* on Circuits, Power and Computing Technologies (ICCPCT-2013), pp.775–781.

DOI: https://doi.org/10.1109/ICCPCT.2013.6528848

Saligram R. & Rakshith T.R (2013). Optimized reversible Vedic multipliers for high speed low power operations. *IEEE Conference on Information and Communication Technologies (ICT 2013)*, pp. 809–814.

DOI: https://doi.org/10.1109/cict.2013.6558205

- Shivarathnamma, Jyothi G. & Kurian M.Z. (2016). A novel approach of 4\*4 Vedic multiplier using reversible logic gates. *International Journal of Advanced Networking and Applications (IJANA)*, pp. 538–542.

- Sridharan K. & Pudi V. (2015). Design of arithmetic circuits in quantum dot cellular automata nanotechnology. *Studies in Computational Intelligence*. Springer, Switzerland. DOI: https://doi.org/10.1007/978-3-319-16688-9

- Srikanth G. & Kumar N.S. (2014). Design of high speed low power reversible Vedic multiplier and reversible divider. *International Journal of Engineering Research and Applications* 4(9): 70–74.

- Subramanian S., Vennila I. & Sudha M. (2016). Design and implementation of efficient reversible arithmetic and logic unit. *Circuits and Systems* 7: 630–642. DOI: https://doi.org/10.4236/cs.2016.76054

- Valinataj M. (2017). Novel parity-preserving reversible logic array multipliers. *Journal of Supercomputing* **73**(11): 4843–4867.

DOI: https://doi.org/10.1007/s11227-017-2057-z